# PGB AZINE

# Get heat relief with low-temperature soldering!

Our library is the bookmobile for the 21st century.

Registered members of **my I-Connect007** have access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to thermal management.

Instead of waiting for the bookmobile, though, our users download new titles with the click of a mouse. It's pretty awesome!

View our eBook library

# PGB007 MAGAZINE

## mSAP and SLP

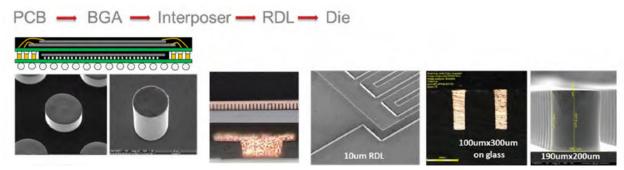

PCBs are now approaching semiconductors with regard to feature sizes. Given this growing trend that shows no signs of slowing down, our experts this month explain substrate-like PCBs (SLP) and the semi-additive processes (SAP) that will help the industry achieve the seemingly impossible (less than 25-micron) features that are coming our way!

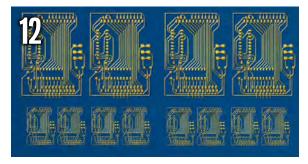

12 Additive Electronics:

PCB Scale to IC Scale

by Tara Dunn

- 18 The Changing Shape of the HDI Market by Roger Massey

- 34 Catching up with...

James Rathburn,

President, HSIO

Technologies

by Dan Beaulieu

44 Smartphone Substrate-Like PCBs

Will Revolutionize the IC Substrate

and PCB Markets

by Emilie Jolivet

# Unrivaled Test Speed with Full Automation

Introducing the newly designed atg A8a with 8 test probes and a new high speed "lights out" automation for unrivaled throughput.

#### **Highlights:**

- Small footprint (6 square meters)

- Dual shuttle pick & place automation

- High accuracy combined with high test speed

- Pen or label marking option

Watch video

**Get more info**

atg Luther & Maelzer GmbH

Zum Schlag 3 • 97877 Wertheim • Germany Phone +49-9342-291-0 • Fax +49-9342-395 10 sales@atg-lm.com • www.atg-lm.com

# PGB007 MAGAZINE

#### **SHORTS:**

- Tags that Turn Everyday Objects into Smart, Connected Devices

- 30 The Electronic Transistor You've Been Waiting For

- 48 'Building Up' Stretchable Electronics to be a Multipurpose Smartphone

- 77 Texas Engineers Work with Uber and Army Research Labs on uberAIR

#### **ARTICLE:**

56 Copper Pillar Plating Systems: High Speed, Low Heat by E. Walch, DJ., C. Rietmann, Ph.D., and A. Angstenberger, Ph.D.

#### **COLUMNS:**

- 8 SLP: The Next Level of Technology by Patty Goldman

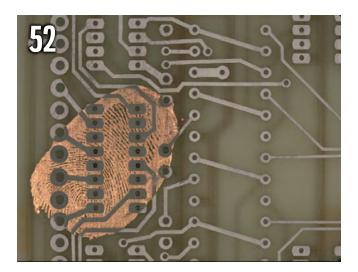

- 52 Understanding Resist Lock-in and Extraneous Copper by Michael Carano

- 74 Global Sourcing: The 5 Cs of Choosing the Right PCB Supplier by Steve Williams

- 78 Meet Nicolas Robin, IPC's New Senior Director in Europe by John Mitchell

#### **HIGHLIGHTS:**

- 32 PCB007 Suppliers

- **50** EINO07 Industry News

- 79 MilAero007

- **82** Top 10 from PCB007

#### DEPARTMENTS:

- **84** Career Opportunities

- 90 Events Calendar

- 91 Advertiser Index & Masthead

## Flexible, reliable Supply Chain Solutions

Ventec International Group is a world leader in the production of high quality and high performance copper clad laminates and prepregs, with full R&D and product development capabilities. Our global distribution means we can readily supply our products to all markets in all geographic areas.

Get your free copy of The Printed Circuit Designer's Guide to...Thermal Management with Insulated Metal Substrates.

**DOWNLOAD NOW**

Ventec - wherever technology takes you, we deliver

Booth 512

**Ventec International Group**

179 Ward Hill Ave, Ward Hill, MA 01835, United States

T: 978-521-9700

E: ordersCA@ventec-usa.com

www.venteclaminates.com

## SLP: The Next Level of Technology

#### Patty's Perspective by Patty Goldman, I-CONNECTOO7

As our electronic devices and machines become more powerful and as Moore's Law chugs along, things in the world of PCBs keep getting smaller. You know the drill—finer lines and spaces, thinner laminates, more layers—cram more circuitry into the same or shrinking area. Where will it all end?

Or will it?

PCBs are now approaching semiconductors with regard to feature sizes, which leads us to our topic this month: substrate-like PCBs (SLP) and the semiadditive processes (SAP) that will help us to achieve the seemingly impossisub-25-micron features that are coming our way. Are you ready? (I can't hear you...ARE YOU READY?)

To help you along that path, our content begins this month with an excellent introduction to the subject by Tara Dunn, Omni PCB, who deals with this technology on a regular basis.

She clearly explains the terminology and the process, step by step.

Atotech's Roger Massey goes into greater depth on the market trends and drivers behind the evolution to SLP. He follows this with a

close look at the newer PCB technology that enables this, including both equipment and chemistry.

To keep you abreast of what's going on in this segment, Dan Beaulieu interviewed James Rathburn, CEO of HSIO Technologies, which is bridging the gap from IC to PCB using liquid crystal polymer technology. HSIO has partnered with an EMS provider to bring their technology to the market. You need to

know about this company.

Elsewhere in this issue, Yole Développement's Emilie Jolivet provides useful market information as you consider how SLP fits with your company's roadmap. First reviewing the evolution of PCBs in smartphones to present day

## **P**pluritec

Celebrating 50 Years of Service!

## The Pluritec brands that provide you with tomorrow's technology today!

X-ray Optimizer & Automated flash/Bevel/Corner rounding panel prep

Drills & Routers 24/7 automation

Multi-color solder mask coaters with 15 minute fast tack oven

MORE INFO

Wet Process developers - etchers - strippers Cobra - MEC Etch Shadow - ChemClean

Mechanical prep Debur - Scubbers - Pumice/Oxide PCB brush & Chemical washing

MORE INFO,

use of SLP technology, Jolivet then projects use in a wide variety of markets.

For those of you out there in the trenches, we have another good troubleshooting column by RBP's Mike Carano, this time on resist lock-in and extraneous copper. As always, Mike provides both cause and action to get you through this problem.

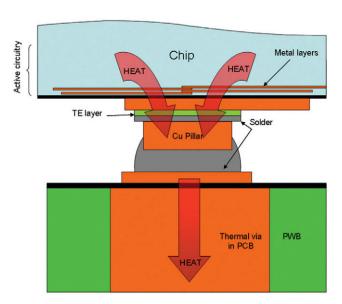

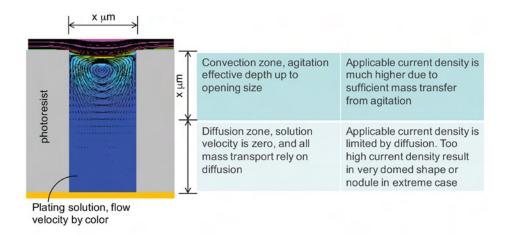

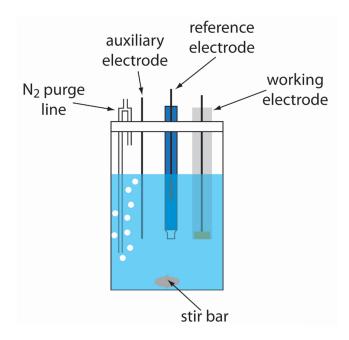

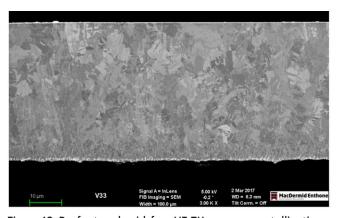

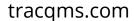

Next, we have an interesting article on copper pillar plating systems. Copper pillars are useful for removing heat from components, but they are not particularly easy to create. MacDermid Enthone's Albert Angstenberger explains both theory and practice for these, as well as delves into via fill and through-hole plating as they relate to the pillar plating.

Bringing up the rear is Steve Williams, The Right Approach Consulting, with a discussion on global sourcing. Whether or not you are involved in choosing PCB suppliers, this article outlines "5 Cs" that truly can apply to any supplier-partner relationship—regardless of which side you are on.

Lastly, IPC's John Mitchell introduces us to Nicolas Robin, IPC's new senior director in Europe. Robin will represent IPC's public policy in Europe, with additional membership-related responsibilities.

Well, folks, this is my last hurrah as managing editor of *PCB007 Magazine*. As I transition to a lighter schedule, Nolan Johnson will be at the helm now. Don't miss his debut in next month's issue that focuses on the automated factory. Not to worry, I won't disappear—at least not yet. I will be managing our quarterly tome, *Flex007 Magazine*, which next appears in late October. Keep your eye out for that—which will be a lot easier if you subscribe. Aren't you going to miss my nagging? **PCB007**

**Patricia Goldman** is managing editor of *PCB007 Magazine*. To contact Goldman, click here.

#### Tags that Turn Everyday Objects into Smart, Connected Devices

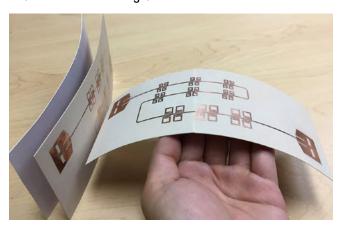

Engineers have developed printable metal tags that could be attached to everyday objects and turn them into smart Internet of Things devices.

The metal tags are made from patterns of copper foil printed onto thin, flexible, paper-like substrates made to reflect Wi-Fi signals. The tags work like mirrors that reflect radio signals from a Wi-Fi router. When a user's finger touches these mirrors, it disturbs the reflected Wi-Fi signals in such a way that can be remotely sensed by a Wi-Fi receiver, like a smartphone.

The tags can be tacked onto plain objects that people touch and interact with every day, like water bottles, walls or doors. These plain objects then essentially become smart, connected devices that can signal a Wi-Fi device whenever a user interacts with them. The tags can also be fashioned into thin keypads or smart home control panels that can be used to remotely operate Wi-Fi-connected speakers, smart lights and other Internet of Things appliances.

"Our vision is to expand the Internet of Things to go beyond just connecting smartphones, smartwatches and other high-end devices," said senior author Xinyu Zhang, a professor of electrical and computer engineering at the UC San Diego Jacobs School of Engineering and member of the Center for Wireless Communications at UC San Diego. "We're developing low-cost, battery-free, chipless, printable sensors that can include everyday objects as part of the Internet of Things."

(Source: UC San Diego)

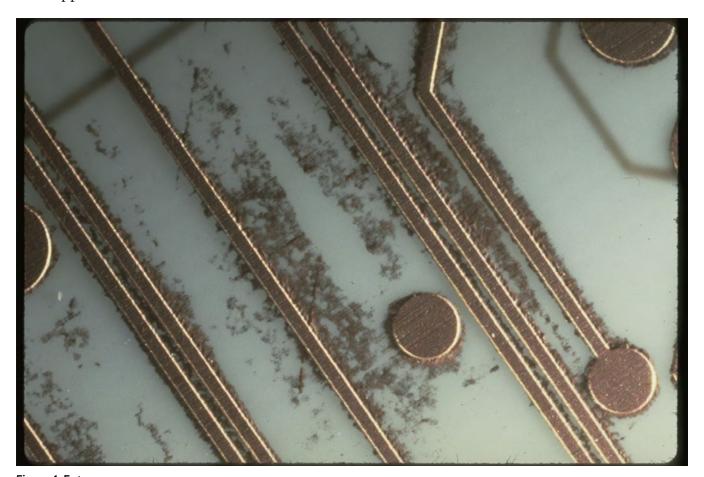

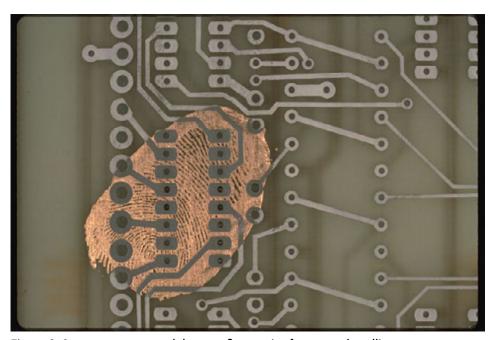

Printed thin, flexible LiveTag tags in comparison with a piece of photo paper (far left). Photos courtesy of Xinyu Zhang

# 5G: Higher Frequencies! Do you have the **right** circuit materials?

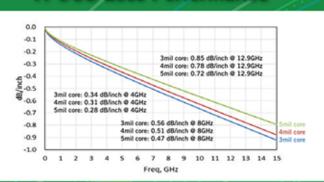

Frequencies at 28 GHz and higher will soon be used in Fifth Generation (5G) wireless communications networks. 5G infrastructure will depend on low-loss circuit materials engineered for high frequencies, materials such as RO4835T™ laminates and RO4450T™ bonding materials from Rogers Corporation!

Rogers RO4835T spread-glass-reinforced, ceramic-filled laminates are low-loss materials in 2.5, 3.0, and 4.0 mil thicknesses. They are well suited for millimeter-wave frequencies as part of the inner cores of 5G hybrid

multilayer PCBs. They can work with other materials to provide the many functions needed by 5G wireless base stations, including power, signal control and signal transfers.

Rogers RO4450T bonding materials are available in 3, 4, and 5 mil thicknesses to help construct those 5G hybrid multilayer circuits. These spread-glass-reinforced, ceramic-filled bonding materials complement the different materials that will form these hybrid circuits, including RO4835T and RO4000° laminates. And for many 5G hybrid multilayer circuits, Rogers CU4000™ and CU4000 LoPro° foils will provide a suitable finishing touch for many hybrid multilayer circuit foil lamination designs.

5G is coming! Do you have the right circuit materials?

Learn more at www.rogerscorp.com/5G

| Product         | *Dk  | *Df    |

|-----------------|------|--------|

| RO4835T 2.5 Mil | 3.33 | 0.0030 |

| RO4835T 3.0 Mil | 3.33 | 0.0034 |

| RO4835T 4.0 Mil | 3.32 | 0.0036 |

| RO4450T 3.0 Mil | 3.23 | 0.0039 |

| RO4450T 4.0 Mil | 3.35 | 0.0040 |

| RO4450T 5.0 Mil | 3.28 | 0.0038 |

|                 |      |        |

Advanced Connectivity Solutions

USA - AZ, tel. +1 480-961-1382 • EUROPE - BELGIUM, tel. +32 9 235 3611 www.rogerscorp.com

<sup>\*</sup> IPC TM-650 2.5.5.5 Clamped Stripline at 10 GHz - 23  $^{\circ}\mathrm{C}$

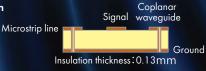

#### Feature by Tara Dunn OMNI PCB

SAP, mSAP, SLP-what kind of crazy acronyms have we adopted now, and how much do you really need to know? In terms of consumer electronics, there is a good chance that the smartphone attached to your hand at all times contains a PCB fabricated with this technology—or at the very least, the next-generation smartphone that you purchase will utilize mSAP technology. In terms of current-day PCB design and fabrication, that really depends on where you are now with technology.

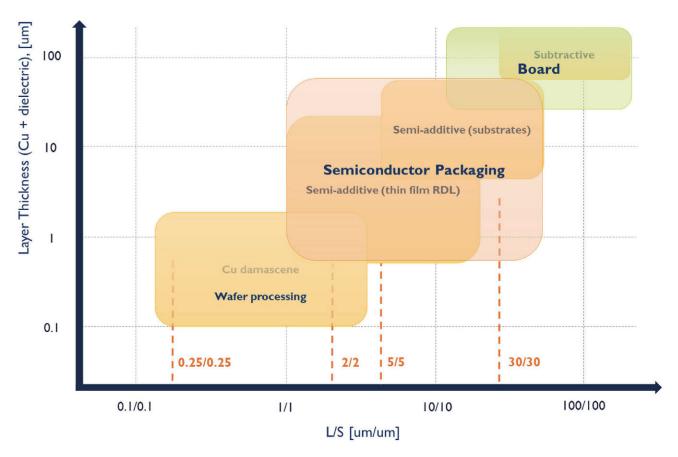

The standard subtractive-etch process serves the industry well. Developments in materials, chemistry and equipment enable the traditional PCB fabrication process to achieve feature sizes such as line and space down to 30 microns. Larger shops with more sophisticated capabilities are building this technology today. Mainstream PCB manufacturing is often limited to 50-75 microns (µm) line and space. But the electronics industry is evolving quickly. Propelled by the demand for more sophisticated electronics, the PCB design is being tasked with finer lines, thinner materials and smaller via sizes. A traditional progression is to first move to HDI technology with microvias and multiple lamination cycles for fabrication. Today's mSAP and SAP technology offers an advanced approach, with line and space capabilities of less than 25 microns, to meet these exceedingly complex design requirements.

#### A Few Definitions

- Subtractive etch process: commonly used to fabricate printed circuit boards. This process begins with copper-clad laminate, which is masked and etched (copper is subtracted) to form traces

- Additive PCB fabrication: this process utilizes additive process steps, rather than subtractive process steps to form traces

- SAP: semi-additive process, adopted from IC fabrication practices

- mSAP: modified semi-additive process, adopted from IC fabrication practices

- SLP: substrate-like PCB; a PCB using mSAP or SAP technology instead of subtractive etch technology

#### Innovation: It's What Leaders Do.

What's next from the leader in flex PCB processing?

- Optimized laser capabilities to improve performance for key applications

- Advanced beam positioning to increase throughput

- Extended laser control to deliver higher yield and productivity

- → New technology to enhance system robustness

- > Combination of high quality and high throughput to lower your total cost of ownership

Focus on Possibilities, Not Limitations.

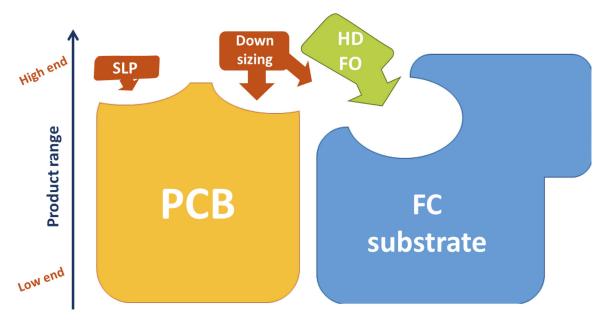

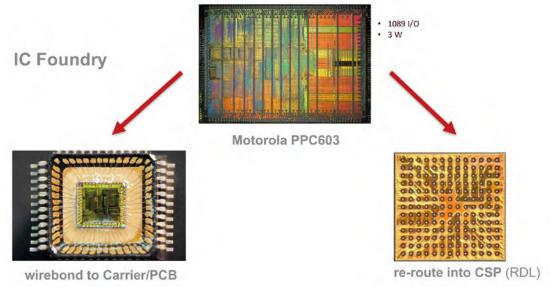

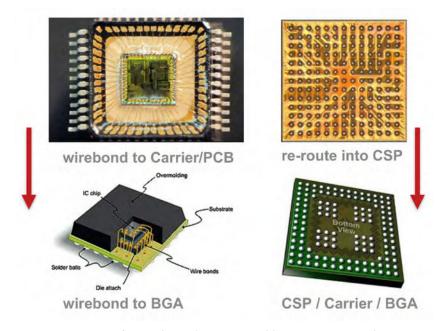

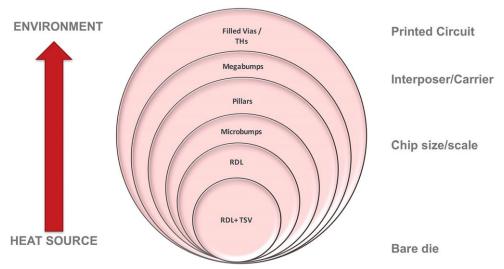

SAP and mSAP are processes commonly used in IC substrate fabrication. As this technology is adapted to and integrated into PCB manufacturing it has the potential to fill a gap between IC fabrication and PCB fabrication capabilities. Subtractive etch PCB fabrication has a limiting factor of finer line/space capability and IC fabrication is limited by a small overall panel size. As these processes are adapted to PCB manufacturing, there is the opportunity to fabricate on larger panel sizes with sub-25micron trace and space.

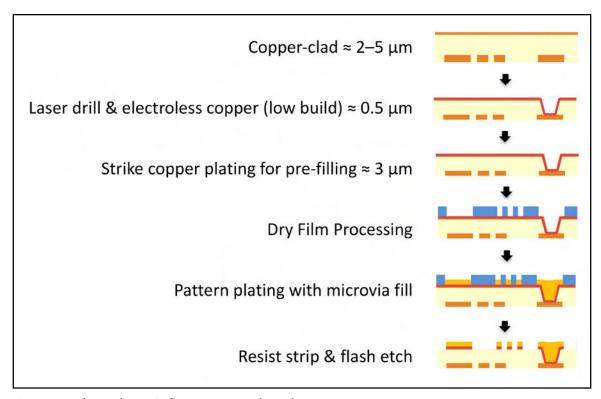

#### In PCB manufacturing, both SAP and mSAP processing start with the core dielectric and a thin layer of copper.

In PCB manufacturing, both SAP and mSAP processing start with the core dielectric and a thin layer of copper. A common differentiation between the two processes is the thickness of the seed copper layer. Generally, SAP processing begins with a thin electroless copper coating (less than 1.5 µm) and mSAP begins with a thin laminated copper foil (greater than 1.5 µm). There are multiple ways to approach this technology and decisions can be based on volume requirements, costs, capital investment needed and process knowledge.

#### The Process

Both the SAP and mSAP, follow a similar process. First, a thin layer of copper is coated on the substrate. This is followed by a negative pattern design. Copper is then electroplated to the desired thickness and the seed copper layer is removed.

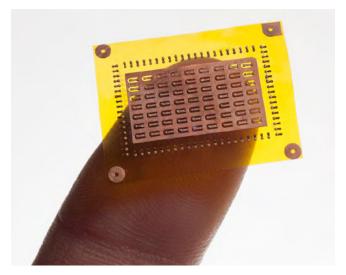

For insight into additive PCB processing steps, I spoke with Mike Vinson, president and CTO of Averatek, a California-based company specializing in a catalytic ink that enables additive processing. He shared information and insight into technology based on Averatek's IP. Averatek's Atomic Layer Deposition (ALD) precursor ink can be utilized for both low-volume and high-volume applications and fully additive or semi-additive processes. The catalytic ink controls the horizontal dimensions of the line width and spacing. The vertical dimension of the metal thickness is controlled by an additive process that deposits metal only on the patterns defined by the photoresist.

Averatek's process consists of six basic steps:

- 1. Drill vias in the substrate using either mechanical or laser drills. (Note: This step is optional if the customer's process includes creating vias after the Averatek process has been completed or does not include vias.

- 2. The substrate is then prepared for processing. In most cases, this is a simple cleaning and mounting of the material in the appropriate material handling system.

- 3. Coat and cure the substrate with the Averatek ALD precursor catalytic ink, resulting in a sub-nano-layer (<1 nm thick) of catalytic material.

- 4. Deposit electroless copper on the precursor. The copper thickness ranges from 0.1  $\mu$ m to 1.0  $\mu$ m.

- 5. Image a layer of photoresist using photolithographic techniques to create the patterns where copper will be deposited. The geometry of lines and spaces that can be produced at this point is anything above 5 µm.

- 6. Electrolytic copper plating will finish out the circuits, followed by stripping the remainder of the resist and flash etching.

This technology enables very fine lines on flexible or rigid substrates, among other materials, at a very competitive cost. Since the holes are plated along with the traces, a smooth and seamless transition can be made. Many of the applications requiring fine-line geometries support high-speed and therefore high-frequency signals, the smoothness and quality of the conducting metal is critical. The process described above produces conductors whose cross-sections are rounded and whose surfaces are smooth. Both qualities are ideal for high-frequency circuitry to minimize crosstalk, shorts, and energy losses.

#### **Markets Utilizing Additive Fabrication**

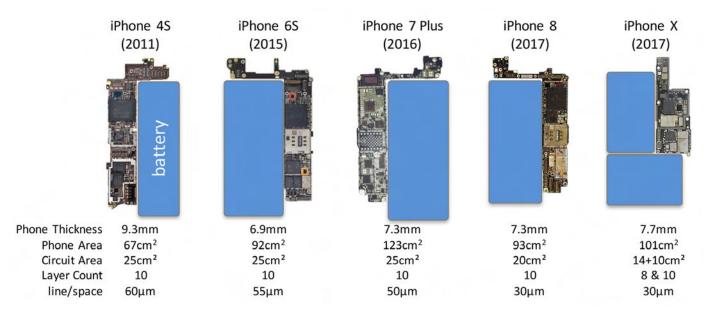

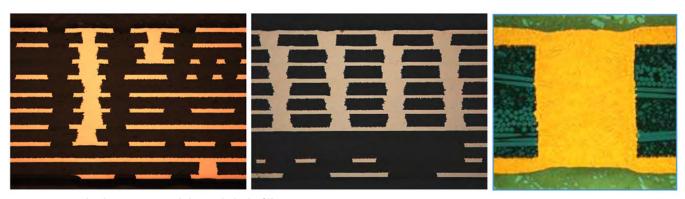

The smartphone market is the most visible market to bring mSAP processes to high volume production, with Apple leading the pack with the launch of the iPhone 8 and iPhone X in 2017 and other manufacturers quickly adopting the technology. Current designs are blending a combination of layers done with subtractive etch and layers with the mSAP technology. mSAP technology allows for a thinner, smaller motherboard design. This was critical to the design to allow more room for the battery and extended battery life for consumers. The technology in the iPhone X reveals 30-micron trace and space (Figure 1). Predictions for the coming years are for trace and space to be in the 10-micron range.

The concept of blending the layers, utilizing the mSAP process for layers with tight pinouts and tough routing, and combining with other layers that are processed with subtractive etch, was proven to be effective in the smartphone market and is spreading to other markets: wearables, medical devices, medical implantables, automotive and aerospace and defense. It is hard to deny the advantages of moving from 10-layer HDI with four-lam-

Figure 1: Motherboard found in the iPhone X. (Source: IFIXIT and Creative Electron)

Figure 2: Circuit fabricated with SAP technology. (Source: Averatek)

ination-cycles designs, to a 6-layer single- or double-lamination design. But, this does force us to look at both design and fabrication in a new way. As fabricators develop processes for this type of requirement, design rules need to be established and reliability testing needs to be completed.

#### **Real-World Applications**

What type of applications are discussing or adopting this new PCB technology? Applications that need extremely thin copper, applications that are concerned with space and weight, and applications that have complex pin-outs pushing the capabilities of traditional PCB manufacturing are all ones that could utilize SAP or mSAP technology.

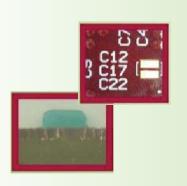

One example is medical implantables using 20-micron trace and space technology, with a double-sided design, on polyimide, with gold conductors. The combination of polyimide and gold is also compelling for biocompatibility reasons (Figure 2).

Military/aerospace applications with highdensity interconnect designs requiring tight pin-outs now have the option of finer lines and smaller vias. Following stack-up structures similar to the work done in the smartphone designs, success is being found domestically by integrating layers with SAP technology and layers with subtractive etch technology, reducing layer count and reducing costly lamination cycles.

Figure 3: Averatek's ALD provides design opportunities with other materials. (Source: Averatek)

Wearable technology is another forerunner. SAP and mSAP enables thinner, lighter weight, more flexible circuity—all attributes catering to the wearable technology market.

Averatek's ALD ink enables printing circuit patterns directly on rounded or unusually shaped structures, including 3D products, the curved end of a catheter and others that the traditional subtractive etch processes have not been able to serve. This ALD ink has also found success in the emerging e-textiles market. Applying the ALD ink to various fabrics and plating with electroless copper results in conductive material that can then be integrated in e-textiles applications (Figure 3). Both these application areas enable design development in growing markets not traditionally served by PCB fabricators.

Recapping, SAP, mSAP and SLP is a process that is currently serving the highly visible, high-volume, smartphone market. The PCB industry world-wide is taking notice and looking for other opportunities to implement this technology in designs with requirements for thin copper, sub 25-micron line and space and

complex HDI designs. This is a new technology pushing fabricators to look at equipment and processes to determine how to adapt from a subtractive process to an additive process. This technology also pushes designers to look at printed circuits in a new way and provides a new tool to solve complex design issues.

I believe pushing us outside of our comfort zone is a good thing, even though it is difficult, and the resulting additional technical capabilities will propel us forward to solve the increasingly sophisticated electronics requirements. Watch for information from SMTA regarding a new conference in 2019, "Additive Electronics: IC Scale to PCB Scale," which intends to address the gap between traditional subtractive etch processing and mSAP and SAP technology. **PCB007**

Tara Dunn is the president of Omni PCB, a manufacturer's rep firm specializing in the printed circuit board industry. To read past columns or to contact Dunn, click here. Electronics Coatings for the Digital Era

### EMP110, Soldermask

- Reputation for reliability

- Meets or exceeds automotive requirements

- Widely used in the automotive industry

T +44 (0)1732 811118 info@electrapolymers.com www.electrapolymers.com

# The Changing Shape of the HDI Market

Feature by Roger Massey Atotech

#### **Evolution of the HDI PCB**

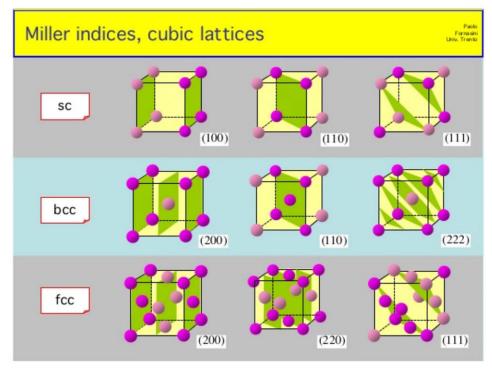

Since their advent in the early-to-mid-1990s, high-density interconnect (HDI) PCBs have undergone several changes and could now be said to be entering their third evolution. Based on subtractive, or print-and-etch processes, the early HDI panels made use of traditional cores and sequential lamination steps to produce highend boards with  $\sim 60~\mu m$  line and space (L/S) capabilities. But most importantly, they relied on microvias to enable their high interconnect density, which, at that time, could not be readily achieved with other technologies.

As board producers improved their processes, HDI board capability also improved; with the release of what we now accept as the smartphone, in the early 2000s, the second generation of HDI panels came into being. While the laser microvias remained, stacked vias began to replace staggered vias, and in combination

with the "any layer" or "every layer" build-up technique, these new HDI boards eventually begin to exhibit  $40 \mu m L/S$ .

Still based on subtractive technologies, this any-layer approach remains the king of the HDI techniques, and it is true to say that the majority of the advanced HDI PCBs that are typical to mobile devices are still produced with this technique. However, in 2017, the HDI market began its next evolution by starting to move away from subtractive processes and into those based on pattern plating. While still reasonably common in Europe and the USA, in Asia HDI has been generally limited to IC substrate manufacturers.

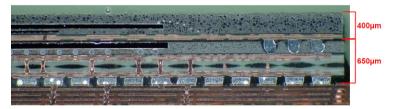

Semi-additive processing (SAP) uses pattern plating processes to realize features < 15  $\mu$ m, and while this size is needed for package substrates, it's not yet called for in advanced HDI boards. However, mSAP and amSAP are modified and advanced modified variations which are now on track to become the next generation of HDI PCBs.

# A new set of rules for PCB production

Less process steps. CAM to etch in minutes instead of hours. Maximum yield. Minimal environmental impact. These are just a few of the PCB production rules that Lunaris has redefined.

We've put together a complete set of all the new rules made possible by Lunaris ...get yours today!

www.mutracx.com

#### **Market Trends and Drivers**

#### Handset Design

As is usually the case, the drive for improvements in PCBs usually comes from the market, and with HDI boards this has really meant changes in mobile handset design.

Looking at Figure 1, we can see an evolution of the mobile phone, and several interesting observations appear:

- Handset thickness has steadily reduced and is currently 7-8 mm

- Handset area has increased, with 90-100 cm<sup>2</sup> now being typical

- Battery size has generally increased in proportion with overall handset size

- Primary PCB area has decreased from approx. 25 cm<sup>2</sup> to 15-20 cm<sup>2</sup>

- PCB layer count has remained pretty constant at approx. 10 layer

- PCB complexity has increased, L/S reduced from 60 μm to approx. 30 μm

So, in order to allow for modern handset design, while leaving sufficient space for all the other components to fit into the handset case, HDI PCBs had to become thinner, smaller and much more complex!

#### Die Packaging

Whilst some of the changes in PCB thickness and area demands can be attributed to handset physical design, which has certainly contributed towards increased PCB complexity, much of the additional complexity can be traced to die packaging needs. And, as many components are now packaged in some form of area array, we need to consider solder ball count, diameter and pitch.

In simple terms, die are more complex than ever, and packaged or not, this generally means they have more I/Os than they had in the past. In order to push I/O count, and still minimize package footprint, one general trend is to try and decrease both solder ball diameter and pitch. At the same time, an increase in I/O count also means more traces are required to route those I/Os, and this can usually be achieved through finer lines, assuming the area and layer count restrictions outlined above are to be followed.

Figure 1 shows the most recent handset designs have a minimum L/S requirement of 30  $\mu$ m, dropping from 50  $\mu$ m in earlier generations. This cannot be achieved with fully subtractive PCB processes as issues during etch become unacceptable, so there is a need to adopt one of the variations of the SAP process-

Figure 1: Evolution of the smartphone. (Sources: iFixit, TechInsights, Teardown.com, IHS, Prismark Partners)

#### **Panasonic**

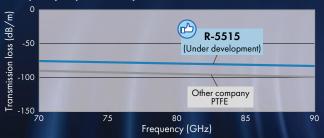

# For Millimeter-wave Band Antennas NEW Material replacement of PTFE

Halogen-free Ultra-low Transmission Loss Circuit Board Material

R-5515

**Under Development**

#### **Features**

- Low transmission loss (Equality or Better than PTFE)

- Dk 3.0 Df 0.0019@10GHz

- Reduce PCB process cost (vs. PTFE)

#### **Transmission Loss**

• Frequency dependence by Transmission loss (70-90GHz)

Transmission loss at 79GHz

| Material           | Transmission loss (dB/m) | Dk (Design) |

|--------------------|--------------------------|-------------|

| R-5515             | 79                       | 3.22        |

| Other company PTFE | 96                       | 3.14        |

Construction

**Contact us**

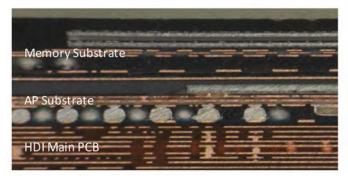

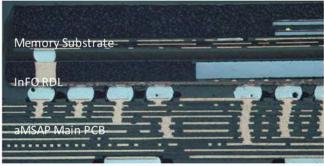

More information

Figure 2: Substrate-based AP package (left); substrate-less AP package using TSMC InFO (right). (Sources: Prismark Partners, left; Atotech, right)

es, which in turn, requires a complete review of the PCB production process.

This recent drive to reduce L/S can be linked to the release of the iPhone 7 in 2016. With the iPhone 7, Apple selected to abandon substrate-based application processor (AP) packages and opted for the new InFO (integrated fanout) package from TSMC.

With InFO, the typical IC substrate is replaced with fine feature redistribution layers (RDL) deposited directly onto the die and package mold surface. Collectively grouped as fan-out wafer level packages (FO-WLP), these package types can offer not only reduced thickness, but allow sub 5  $\mu$ m L/S to be applied in the RDL, enabling an appreciable increase in I/O count, and with the associated reduction in pad pitch, this can occur without sacrificing real estate; more importantly, all of this is

achieved while maximizing electrical and thermal performance which are critical in modern smartphone designs.

#### **PCB Technology Trends**

Outside of packaging, there are a number of other trends going on within PCB production, all of which impact critical steps of manufacture, and will affect HDI design going forward.

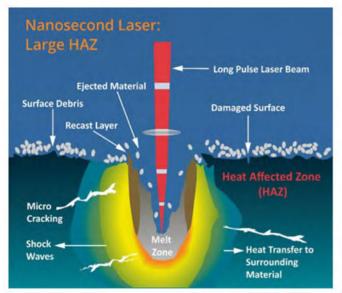

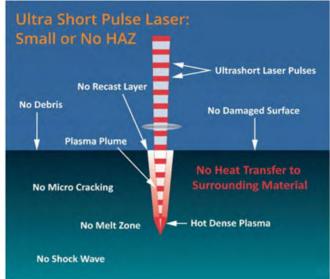

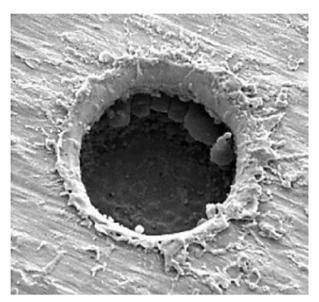

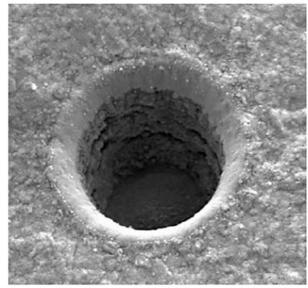

Using established tool sets, the majority of today's microvias are formed by CO<sub>2</sub> lasers. One negative of the process is appreciable amounts of heat generated within the substrate, which leads to the formation of a heat-affected zone (HAZ) at each drill site, which impacts minimum via pitch as well as their size and quality.

In order to resolve this, laser manufacturers are developing new tools with ultra-short pulse (USP) lasers, which replace the existing nano-

Figure 3: Impact of laser pulse duration on HAZ. (Source: IPG Photonics)

## Excellon

Manufacturers of precision Micro-Machining Solutions for over 50 Years

**COBRAII**

Hybrid laser system

689

6-station precision drilling and routing system

**HS-1L DS**

Single-station, dual spindle high-speed system

136L

High accuracy and speed

154L

Large panel applications

HS-2L

2-station, high-speed

129

Single-station precision system

Move into the future with the latest innovations in Fabrication Technology from the Industry Leader!

Figure 4: Typical microvias formed with nanosecond laser (left) and USP laser (right). (Source: Orbotech)

second pulses with picosecond or femtosecond pulses. These offer not only smaller vias but do so with a much smaller HAZ, meaning microvia pitch can be greatly reduced and as laser absorption is improved, the resulting vias are of a much better quality with less surface debris or "splash." As these laser systems become available, the capability of microvia density will take a step improvement, enabling another jump in HDI capability.

Once the microvias are formed, the next issue becomes plating, and while vias have not had dramatic changes in aspect ratio, typically maintaining 0.7-0.8, they have steadily reduced in size, which has led to challenges in plating. One important development has been the ability to fully fill vias with copper, which has enabled the stacking of vias directly on top of each other. This has been so influential that stacked

vias are an integral part of HDI design as they enable space savings, especially over the older staggered vias, improved thermal and electrical management, and their superior surface planarity also contributes to final assembly yields.

One recent plating development has been the release of processes for through-hole filling (THF). Solid columns of copper will improve thermal conductivity in heat-critical areas allowing for improved cooling and THF potentially supports increased I/O density as via-inpad is still possible.

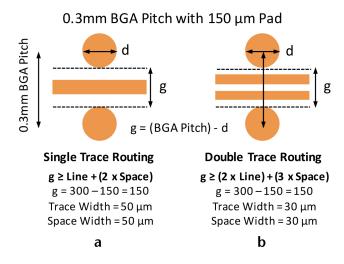

#### **BGA Design Rules**

As in many cases, the critical design parameters for an item are often linked to other aspects within that design, and HDI PCBs are no different. In this case, some of the controlling factors are the BGA pad size and pitch.

Figure 5: Stacked microvia and through-hole filling.

| Number of Traces | Required Line / Space Width                            |  |

|------------------|--------------------------------------------------------|--|

| 1                | g ≥ Line Width + (2 x Space Width)                     |  |

| 2                | $g \ge (2 \times Line Width) + (3 \times Space Width)$ |  |

| 3                | $g \ge (3 \times Line Width) + (5 \times Space Width)$ |  |

Table 1: L/S required for given pad dimensions.

Looking at Table 1, we can see the relationship between solder pad dimensions and possible trace widths, depending on the number of traces required to pass between the pads. For a "simple" or low I/O count package (Figure 6a) where we only need to route a single trace in-between the BGA solder pads, it's clear that the maximum trace width is 1/3 of the available space between the pads. In the example shown, we have  $300~\mu m$  pad pitch, with  $150~\mu m$  pad diameter, resulting with a recommended line and space requirement of  $50~\mu m$ .

If we now use a more complex package where the higher I/O count requires that two traces need to route through the same pad spacing, the recommended L/S drops to 30  $\mu$ m, and it's obvious that as pad pitch decreases, this will apply further restrictions for line width and separation.

As a general summary, the availability of new laser tools will allow for smaller microvias that will be closer together. This will help enable the use of smaller solder pads on the BGA,

Figure 6: Effect of trace count on dimensions. (Source: Altera)

and in combination with higher I/O count devices, will drive the demand for a reduction in line and space requirements, which will push the HDI roadmap (Figure 7) and continue the move from the existing every-layer production routes into the variations of the semi-additive processes.

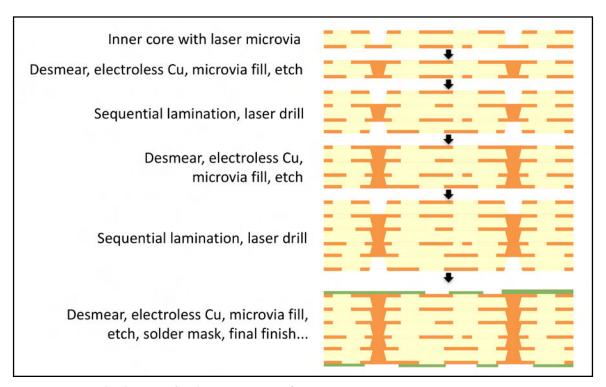

#### ELIC, Any-Layer and mSAP

The majority of HDI PCBs are currently produced using a subtractive ELIC (every layer interconnect) or any-layer technique. The general process flow is outlined in Figure 8.

There is a demand for high-end HDI PCBs to move from 40  $\mu$ m L/S down into the region of 30  $\mu$ m, and as this can not be achieved with

|                        | 2015        | 2016 | 2017       | 2018 | 2019 | 2020        |

|------------------------|-------------|------|------------|------|------|-------------|

| μVia Diameter (μm)     | 7           | 0    | 5          | 0    | 40   | 0           |

| μVia Aspect Ratio      |             | 0.8  |            | 0.9  | 1.   | 0           |

| μVia Pad Diameter (μm) | 200         | 140  | 140        | 130  | 120  | 100         |

| Min L/S (μm)           | 35/35       |      | 25/25      |      | 20/  | <b>'</b> 20 |

| Cu Thickness (µm)      | 15          | 12   |            | 10   |      | 8           |

| BGA Pitch (μm)         | 350         | 30   | 00         | 250  | 20   | 00          |

| Technology             | Subtractive |      | mSAP/aMSAP |      |      |             |

Figure 7: Critical factors within the HDI Roadmap. (Sources: IPC, Jisso, Atotech, customer base)

Figure 8: General schematic for the ELIC process flow.

Figure 9: Outline schematic for SLP process based on mSAP.

the current panel plating process, a switch to semi-additive processes is required. With these processes being common to IC substrate production, the resulting HDI boards are becoming known as substrate-like PCBs (SLP).

A generic process flow for SLP production based on mSAP techniques is shown in Figure 9.

## Having trouble keeping up with front-end demand? **We have people for that.**

Here are six ways that outsourcing CAM and related front-end work can help manufacturers not only stay in business but also help them thrive:

- Increased on-demand capacity

- Improved automation

- Faster turn-around times

- Reduce costs

- Improved quality

- · Ability to build redundancy in critical areas

We deliver the highest quality PCB CAM and Mechanical CAD engineering services to customers around the world.

Find out how we can help you >

#### **Process Challenges**

It is clear that the mSAP processes share common steps with the more traditional PCB production routes, so in principle it would appear to be quite straightforward to update and stretch existing facilities in order to make the change from subtractive to mSAP production. However, due to many of the changes involved, it is typically seen as simpler, and as has been proven recently by those vying to enter the SLP supply chain, certainly better to make the required investment into new equipment and processes which are tailored to the mSAP approach. One obvious concern after such an investment would be the expected lifetime of the mSAP processes. Fortunately, these can be further revised into an amSAP approach, which enables > 20 µm L/S with limited further investment being required.

Table 2 shows a simple comparison of the technologies available, including their capabilities and major differences.

For those looking to enter the SLP supply chain and begin to provide suitable boards, there are a number of challenges that need to be overcome, some of which can be resolved through investments, others which can only be achieved through working with experienced process suppliers.

#### **Improved Laser Drilling**

While the new generation of laser drill tools will surely arrive in due course, the current CO2 machines will remain the workhorse of microvia processing for some time. Updated for compatibility with the reduced foil thickness used in mSAP, chemical processes can pretreat Copper surfaces to maximize CO2 laser absorption and achieve improved hole shape, while ensuring the best possible conditions for subsequent plating operations

#### Optimized PTH

Reliable PTH coverage in microvias is critical to not only mSAP production but the anticipated reduction in via dimensions, along with a broadening range of dielectric materials, means that the electroless copper processes will also require review. Robust activation systems combined with optimized pretreatment systems will be required to work with high throwing power electroless copper baths to ensure via coverage, be that in vertical or, as is more common, horizontal tool sets.

#### Pattern-Plated Copper

Filled vias, be they full through-hole or stacked microvias, are essential to modern mobile PCB designs. However, for SLPs via fill must be achieved along with fine line pattern plating and excellent surface uniformity, all within acceptable plating times.

#### Fine Line Formation

< 30 µm lines require fine line imaging processes not typical to subtractive processing.

|                              | Subtractive     | mSAP      | amSAP | SAP          |

|------------------------------|-----------------|-----------|-------|--------------|

| Achievable L/S (μm)          | > 35            | > 30      | > 20  | 9/12         |

| Cu clad thickness (μm)       | 2–9             | 2–5       | < 3   |              |

| E'less Cu thickness (μm)     | 0.35-0.50       | 0.35-0.50 | 1     | 1            |

| Flash Cu thickness (µm)      | 2–5             | 1–3       |       |              |

| Panel plating thickness (μm) | 15–20           |           |       |              |

| Pattern plating required     | No              | Yes       | Yes   | Yes          |

| Etch resist                  | Dry film or LER |           |       |              |

| Cu to be etched              | 17–29           | 4–10      | < 3   | 0.7-1.2 (Rz) |

Table 2: Outline comparison of PCB production techniques.

# Your Passport to Global PCB Sourcing

We are pleased to announce that with the same fine service, quality, delivery and attention to detail that our customers have grown to rely upon, we are now adding a complete global solution to meet all of your needs, both today and in the future.

#### **Our Solutions:**

- FLEX & RIGID-FLEX

- HDI / MICROVIA

- COMPETITIVE VOLUME PRICING

- PRE-QUALIFIED OFFSHORE PARTNERS

- QUICK-TURN PROTOTYPES

- COMPLEX MULTILAYER

- MIL-SPEC PRODUCTION

- SPECIALTY MATERIALS

Low etch surface preparation aids with dry film adhesion, novel resist strippers are needed to ensure no film residues, while controlled etch processes must be able to form the final patterns without excessive undercut or track width loss

#### Improved Layer Bonding

With finer patterns, higher track densities and the push for higher operating frequencies, SLP processes must minimize copper removal and maximize signal integrity through low surface roughness where possible.

#### **High-Resolution Surface Finish**

With finer features across the SLP, the final finish must also ensure compatibility, and in most cases this means no extraneous plating (nickel foot). This, in combination with enhanced corrosion resistance and controlled gold thickness, makes the new generation of ENIG chemistries the preferred solution for high-end PCB applications.

#### **Summary**

With more mobile device designers looking to utilize the benefits of FOWLP and other direct attach package types, a new generation of HDI PCBs is already in the market. Targeting  $<\!30~\mu m$  features and based on mSAP techniques, these substrate-like PCBs make use of the latest high-end manufacturing processes and materials, to enable the next evolution in advanced HDI boards.

Chemical and material suppliers are realigning processes and products from the packaging industry and adjusting them to fit into this new SLP sector, while prospective SLPs producers are reviewing their existing processes and deciding if they should invest. As some will inevitably decide against the investment, will we risk a limit in the future numbers of players in the SLP supply chain? Only time will tell, but the advanced HDI market is again facing a new challenge, but one we can surely rise to meet. **PCB007**

**Roger Massey** is technical marketing manager at Atotech GmbH.

## The Electronic Transistor You've Been Waiting For

How do you pack more power into an electric car? The answer may be electronic transistors made of gallium oxide, which could enable automakers to boost energy output while keeping vehicles lightweight and streamlined in design.

A recent advancement—reported in the September issue of the journal *IEEE Electron Device Letters*—illustrates how this evolving technology could play a key role improving electric vehicles, solar power and other forms of renewable energy.

"To advance these technologies, we need new electrical components with greater and more efficient power-handling capabilities," says the study's lead author Uttam Singisetti, PhD, associate professor of electrical engineering in UB's School of Engineering and Applied Sciences. "Gallium oxide opens new possibilities that we cannot achieve with existing semiconductors."

The most widely used semiconducting material is silicon. For years, scientists have relied upon it to manipulate greater amounts of power in electronic devices. But scientists are running out of ways to maximize silicon as semiconductor, which is why they're exploring other materials such as silicon carbide, gallium nitride and gallium oxide.

While gallium oxide has poor thermal conductivity, its bandgap (about 4.8 electron volts) exceeds that of silicon carbide, gallium nitride, and silicon.

Bandgap measures how much energy is required to jolt an electron into a conducting state. Systems made with high-bandgap material can be thinner, lighter and handle more power than systems consisting of materials with lower bandgaps.

(Source: University at Buffalo)

#### JOIN IPC'S JOB TASK ANALYSIS COMMITTEE

Make sure your voice is heard on the critical issue of skills gap in the electronics manufacturing industry. Help IPC define the workforce skill requirements needed for today and the future.

Join **IPC's Job Task Analysis Committee (JTA)** to help address the skills gap and provide training and career opportunities for your employees.

#### Why Join JTA?

- To address the skills gaps in your own company.

- To ensure that your staff will be well trained moving forward.

- To decide which jobs need focus and which skills are most important for your industry.

Help us help you shape IPC education and certification offerings that keep your company moving forward and improve recruiting and retention.

For further information, please contact **Dave Hernandez**, senior director of learning and professional development, at **davidhernandez@ipc.org**.

#### **Gardien Launches Largest Operational** Tester in the World ▶

Gardien Group debuts G90 XXL—the biggest operational tester yet in North America. With a maximum board size of 63" x 47.2" (1600 mm x 1200 mm), this premium double-sided flying probe system is set to create a revolution in the industry.

#### **Ventec International Group Appoints** Jason Chung as CEO >

Ventec International Group Co., Ltd. announced that its board has elected Jason Chung as group CEO with immediate effect. Chung succeeds Tony Lau who continues in his role as chairman of board of directors.

#### **American Standard Installs** Hitachi Drill

American Standard Circuits has recently acquired and installed a Hitachi Drill Model ND-6Y210E. The Hitachi ND-Y series demonstrates high-speed and high-precision drilling powered by an advanced servo system.

#### **Punching Out! Beware of Customer** Concentration Risk

One of the biggest risks in M&A is customer concentration risk. It is hard to avoid as a business owner; if a customer is giving you orders, you generally take them! The next thing you know, your customer has 90% of your sales and they own you. We see this a lot in both the PCB and contract manufacturing industries.

#### **Circuit Automation on the Ever-Evolving** World of Solder Mask

In a recent conference call, I-Connect007 editorial team was joined by Circuit Automa-

tion's Yuki Kojima, VP of engineering; Larry Lindland, sales and applications manager; and Tom Meeker, CEO, for a lively discussion about solder mask. Spoiler: It's not all about the equipment.

#### First EIE Technology at Royal Circuits

Royal Circuits Group has furthered its investment in First EIE process equipment, acquiring a direct image system for its facility in Southern California, and inkjet technology for the Hollister, Northern California location.

#### Agfa: Staying Ahead of the Technology Curve ►

In the ultracompetitive electronics manufacturing space, companies that don't continually evolve and invest in new technologies run the risk of being left behind. At the recent EIPC summer conference, many next-generation processes and technologies were discussed and even put on display.

#### **A-Gas Electronic Materials Acquires** Elga Europe >

A-Gas Electronic Materials have acquired all the assets of Elga Europe of Daventry in Northamptonshire. Elga Europe is the sole dry film distributor of Ordyl film in the UK, which is used extensively in printed circuit board manufacturing and currently produced and slit in Milan at Elga Srl.

#### **R&D Altanova Chooses Ultra-Precision** atg S3-8 - Flying Probe Technology for High-Speed Electrical Test of Substrate Products >

atg Luther & Maelzer GmbH, confirms delivery of high-speed bare board testing technology to R&D Altanova.

### Integrate QA Solution

Because everyone's QA needs are just a little bit different.

Integrate is a fully customized solution, and no two contracts are exactly the same. No matter what size customer you are, we can tailor AOI, testing, final inspection, or a combination of all three services to fit you. And you only pay for the product that actually passes quality assurance, not on panels produced or tested.

Find out if our Integrate solution is right for you! www.gardien.com/why-integrate

# Catching up with... James Rathburn President, HSIO Technologies

#### Feature by Dan Beaulieu

I love innovative companies and keeping up with what they are doing. One of the most creative and innovative companies in our industry is HSIO Technologies, founded by entrepreneur and inventor James Rathburn. Based in Maple Grove, Minnesota, this company stays at the cutting edge of the electronics industry's technology. Leveraging extensive interconnect device knowledge with proven semiconductor fabrication, printed circuit fabrication, and microelectronic assembly processes enables them to quickly develop cost-effective, high-performance interconnect solutions across a wide variety of form factors. I checked in with Jim recently to see what he and his team are up to and learned how they are using liquid crystal polymers and other materials to focus on increasing high-speed and high-density PCBs for uses in all markets.

**Dan Beaulieu:** Jim, for the readers who might not be familiar with HSIO, tell us a little bit about it.

**James Rathburn:** I founded the company in 2010 and launched it with an investment from partners from a previous company called Gryphics Inc., which we sold in 2007. The previous company produced high-performance test sockets for the semiconductor industry. The customer base

was reaching a point where the signal integrity of the system PCB and package substrate were defeating the performance of the high-speed sockets. The plan was to create an integrated technology that would include high-speed printed circuits with low-loss connectors, to mate them. We started HSIO by going to our customer base and asking, "If you could have new technology developed, what would that be?" The common theme was that they needed finer lines and spaces. They also said that vias were killing their signals. So, from that came our charter at HSIO which was to come up with a new way to look at fabricating printed circuits with finer lines and spaces and signal integrity as the focus.

**Beaulieu:** What are some of the ways you are meeting those challenges, with respect to technology at HSIO?

**Rathburn:** We are in the process of commercializing a printed circuit technology we have developed utilizing liquid crystal polymer technology. The technology is not limited to LCP, and we can utilize conventional materials, but LCP is the focus for high-speed and high-density. We developed the technology in our Minnesota and Arizona operations and have established a manufacturing relationship with Benchmark Electronics to scale production and

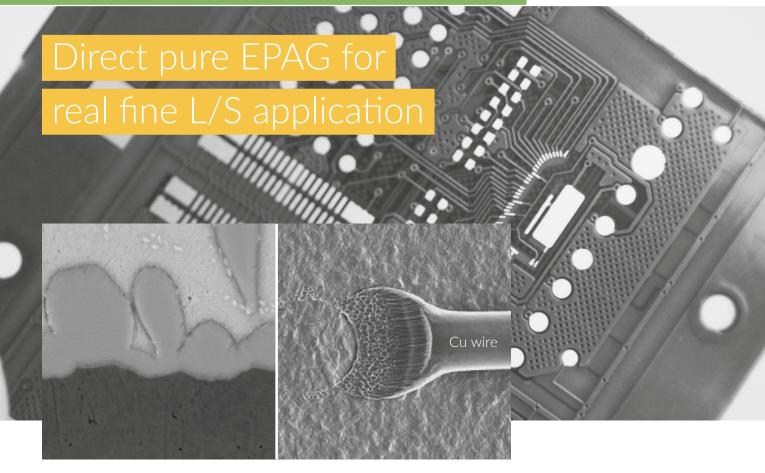

#### PallaBond®

Premium soldering and wire bonding capability

IMC investigation 0.1 μm Pd / 0.1 μm Au Top view: copper-wire 20 µm on EPAG finish

PallaBond® is an environmentally friendly process suitable for high frequency and fine L/S applications. The process provides very good bonding capability with aluminum-, gold-, silver-, copper- and copper-palladium-wires. Especially outstanding is its good solder joint reliability.

Thanks to its very mild process conditions, it provides excellent compatibility with base materials and soldermasks. It also consumes less energy and water than ENIG, ENEPIG and immersion tin finishes.

4

Bio compatible pure palladium ideal for medical application

Atotech Group +49 30 349850 info@atotech.com

Global head office atotech.com

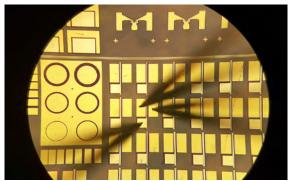

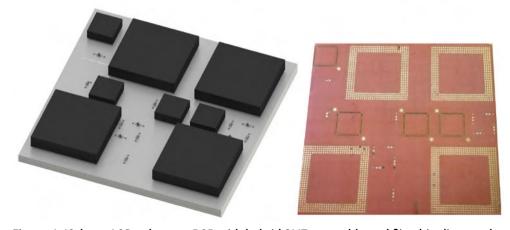

Figure 1: 12-layer LCP PCB with hybrid rigid core and LCP high-speed signal layers.

support engineering and application development. Benchmark is launching full production with the RF High-Speed Design Center of Innovation, circuit fab, micro-electronics assembly, SMT assembly and test—all within the same process flow, all focused on next generation high-speed and RF technology needs. We are very proud to be part of this effort, which has never been done this way in the EMS industry. We work directly with the Lark RF Technology subsidiary of Benchmark, and Daniel Everitt, Benchmark's VP and GM of Lark, will be presenting at the upcoming EDICon conference in October.

**Beaulieu:** Why did you choose to go in this direction?

**Rathburn:** The original development plan was to create a circuit-plus-socket technology family with tuned performance for the semiconductor test customer. Historically, the chip producer tests the device to make sure it will function properly in the final system. Typically, the signal integrity requirements for test have been much more stringent than actual system use to make sure everything in the system works together. As system performance and complexity has evolved, in many cases it is no longer good enough to test outside of the actual usage model. This development has evolved further

to the point where many end systems need to have the performance previously needed only at test. Our technology can provide the best performance in both test and commercial markets. In the end, the purpose of the technology is to provide a new way of designing and fabricating high-performance printed circuits with high-density.

**Beaulieu:** What markets are interested in using this technology?

**Rathburn:** One of the most exciting aspects of the technology is the various markets it can apply to. In the past, the mil/aero/defense/satellite/space/test industries were the main drivers of RF and MW technologies. In the world we have today and in the pending future, highspeed digital, mobile/wireless, automotive, low-power mixed signal, and analog technologies all kind of need the same precision circuitry fabrication techniques. From aerospace and defense, to consumer electronics, to medical markets, the principles of size reduction with performance improvement available from a company like Benchmark that can design, produce and test volume is very compelling. The best part from a design perspective is the technology is basically the same regardless of the market.

Additionally, there is a broad range and mix of industries we are working with. The milaero/ defense industry is probably the area that has lacked this type of capability to date and there is a large focus in the community towards heterogeneous integration and advanced packaging. These types of engagements typically start with an incumbent technology with evaluations as to how to make the existing better near term then explore longer term qualification with a more integrated approach. Highspeed data, processing, memory, wireless/RF applications all have interests that are much shorter life cycles and driven by systems and silicon development.

With the onset of 5G deployments, smart vehicle and automotive communications, flexible displays, high-speed data/optical processing and storage along with the mil/aero needs,

I call the future a technology convergence. All those industries need the same technology, just in a different configuration, scale and volume. Everyone needs to worry about highspeed signals, power requirements, thermal management, physical size, cost, antennae, filters and mixed-technology hybrid assembly. LCP is also rather unique in that it has low moisture absorption and has the potential for exposed environments, hermetic applications and implantable medical devices.

Most of our efforts currently are aimed at characterization with design rule and manufacturing refinement out to 110 GHz RF and 112 GB digital. As with any new technology, there is a period of time required for dialing in the design rules and refining the production processes needed to ramp volume capability. Long-term reliability requirements vary greatly from market to market and that is of key interest to all. Component obsolescence in the mil/aero industry has also become a major issue. By the time a program launches, oftentimes one or more silicon nodes have passed the technology by and there is significant interest in the ability to take state of the today's technology components and arrange them in a meaningful way that fits into a legacy platform without full requalification.

**Beaulieu:** Jim, let's dig a little deeper. What can you tell me about the some of the specific capabilities of your products?

**Rathburn:** When you look at the current line and space capability in the domestic supply base, there are many companies that can produce high-quality 3- to 4-mil line and space multilayer circuits. There is a challenge to produce high-speed multilayer boards with very tightly controlled impedance below 2-mil line and space with conventional materials, and there has been a domestic supply chain gap. LCP has been around for many years but has suffered from reliability and density challenges with multilayer applications. The production launch capability can fabricate 1-mil or 25-micron line and space LCP circuit stacks with up to as many 20 layers in flex, rigid-flex, sub-

strates, modules and multilayer boards. We are also launching our next generation technology that pushes the line and space capabilities to nine microns, with added capabilities like embedding coaxial signal lines, embedding active and passive components and high-speed functional test at the die level during assembly.

**Beaulieu:** Tell our readers something about your and the team's expertise.

**Rathburn:** Our expertise at HSIO is fundamentally electrical interconnects but extends to understanding how our customers need to interconnect everything in a system, not only today but in the future. The next step is to create a technology that is based on sound manufacturing processes but also not just another version of what is already available. The material LCP has some great properties, but it is the way it is used as part of the manufacturing process that

Figure 2: Cross-section of 12-layer LCP rigid-flex with solid full metal microvias.

is the key. The ability to take advantage of the process capabilities with design and application expertise to help customers convert traditional designs or create brand new ones is critical to market acceptance as well. This is what the Benchmark relationship is all about.

**Beaulieu:** One of the things I always look for in a company is what makes them outstanding. What is it about HSIO that makes them outstanding?

**Rathburn:** Our technology has been very wellreceived by an impressive list of customers across many market segments. The engineering communities can solve challenges and create new ways of integrating electronics components into a package, or higher-level assembly. Traditional high-performance materials are typically expensive and actually reduce the density of interconnect in many cases when pushing to higher frequencies. Our approach allows for higher-tuned performance while increasing the density and reducing the effective product size. The ability to embed components that are normally surface mounted is a large focus for the future. Benchmark is enabling the entire capability chain to help customers with engineering expertise focused to take best advantage of the technology from concept, through production, as far as the customer would like to go, all the way to system and box build. Many customers can envision multiple generations of integration with enhancements rather than brand new design, which is very significant from a time-to-market and development standpoint. We believe that once the technology is adopted, there is no going back to previous generations with conventional materials and methods. I think what makes HSIO stand out is we have very good relationships with the test and development groups within the leading semiconductor companies. Our products are used to test many of the future chips 1-3 years before the devices that use those chips enter the market. We see the system requirements driven by the next-generation chip technology needs long before any printed circuit supplier

Figure 3: Cross-section of coaxial signal lines embedded in LCP circuit stack.

or EMS company would. Providing the technology and high performance needed for silicon validation and system level test and enabling those capabilities in volume production end-product use is a major goal of the Benchmark-HSIO relationship.

**Beaulieu:** Where do you rate HSIO's products and technology compared to the competition?

**Rathburn:** Our main competition is the conventional material sets and design rules. Most engineering teams would rather extend what is already being produced to meet the next generation requirements. Another competitive aspect is that LCP as a material has been an elusive treasure that has a bad reputation for being difficult to process, hard to control, and unreliable in the field. Volume use within the cellphone market in recent years has helped overcome reluctance and our technology demonstrations are possibly the most impressive LCP products built.

The technology convergence I mentioned is creating multiple roadblocks across multiple industries; that is a huge challenge, but also a significant opportunity. As signal speeds and frequencies jump from today to multiples of today in the next couple of years, it is not only important to function at the desired base frequency, but the accuracy of the circuits in the band around that frequency is equally, if not more, important. Our philosophy is "every micron matters" and that is truly the case

**Etchers**

**Scrubbers**

**Developers**

PTH

**Oxide Replacement**

THIN CORE HANDLING • PC CONTROL • RELIABLE • LOW COST

**CLICK TO VIEW OUR UCE WET PROCESS LINE**

The leading European PCB Equipment and Parts Supplier

www.vikingtest.com sales@vikingtest.com

when tuning very fine, high-density circuits in a stack that may have 12 to 20 layers. Traditional PCB suppliers in the U.S. often still communicate in mils and have a somewhat experience-based view of build-to-print and acceptable geometries. At the same time, if the application can get by with 3-mil lines and spaces on polyimide or FR-4, then we are not the right fit. Many of the industry publications and conferences highlight state-of-the-art modified semiadditive substrates or wafer level fan-out packaging for high-volume applications. We believe our technology has the right mix of fine lines, impedance control, layer count and the expertise Benchmark provides for engineering, production, assembly and integration that is found nowhere else.

**Beaulieu:** Now let's talk about quality. Let me know what qualifications, certifications and registrations you have and why these give you an advantage over other companies.

**Rathburn:** One of the challenges HSIO faced as a company developing promising technology is that the engineering teams have interest and the ability to experiment and explore, but commodity and production teams need a viable, strong supplier base to even consider important components. Historically, customers in the test and development world are less concerned with volume production, certifications, ISO registrations and that is the market HSIO has served directly in the past. A key advantage of the Benchmark relationship is

they are a respected tier EMS company that has the strength, reputation, qualifications and resources to support customers across most markets with all of the commercial requirements along with the leading-edge technology and capability that sets them apart from commodity PCB assembly and box build.

**Beaulieu:** Jim, I know that much of your work is considered research and development; can you talk about that?

**Rathburn:** Our R&D work is typically driven by a specific customer need that can be applied to multiple customers and multiple markets. We try to avoid science projects that are for the sake of R&D and focus on process development that can help us make something meaningful. We are launching the LCP technology product at the 25-micron range node and that is a significant improvement with multiple shrinking of conventional technology and significant opportunity.

The focus of our current R&D efforts is what I call Direct Die Attach LCP. The principle is to arrange packaged components without the substrate or interposer and attache the die directly to an LCP module. The evolution is to shrink the current PCB assembly with an LCP PCB, then shrink one step further with direct die attach. The DARPA CHIPS program has a similar philosophy to disintegrate an ASIC device into chiplets that can be assembled onto a substrate and offers the capability to include mixed semiconductor technology beyond monolithic silicon. Our parallel R&D effort is the ability to test these devices at speed as a connected group before they are assembled, while they are being assembled, and after they are assembled. Known good devices are important in this type of assembly, and critical if devices are embedded within an assembly with no possibility of rework.

Figure 4: 10-layer LCP substrate PCB with hybrid SMT assembly and flip chip die attach.

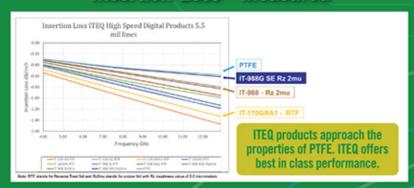

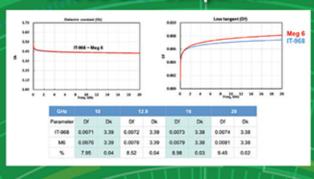

## IT-968 / IT-968 SE

High Thermal Reliability

Designed for High Speed Digital Applications

- Telecom, Backplane, Base Station, Server, Storage, Switch IT-968

Dk @ 10 GHz - 3.85

Df @ 10 GHz - 0.0043

**IT-968 SE**

Dk @ 10 GHz - 3.30

Df @ 10 GHz - 0.0019

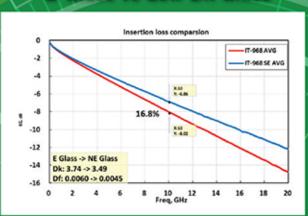

#### Insertion Loss - Measured

Industry Test Vehicle

32 layers, 0.140" thick

Four 2 oz copper internal layers

0.8 mm pitch, 9.8 mil drills

- Passed 1000 hours CAF, 10 V bias, 50 V

- IST Passed 1000 cycles, 6x 260°C precondition

- No delamination after 8x 260°C reflow after 2 weeks at 35°C/ 85 % RH

#### IT-968 Loss Performance

#### IT-968 SPP Comparison

#### Ultra Low Loss IT-968 SE

#### E-Glass vs Low Dk Glass

Figure 5: Benchmark's RF High-Speed Design Center, circuit fab, and assembly operations.

Beaulieu: What are your plans? Where, for example do you want to be in five years?

**Rathburn:** The short answer is five years away seems too far away to predict. The drive for silicon node shrinks appears to be more challenging and yield curves difficult to manage. When I look at today's state-of-the-art electronics, there are extremely complex silicon devices surrounded by hundreds of less complex devices and connected with large connectors. We have many patents, applications and disclosures related to high-speed interconnects that can not only improve the performance and shrink the PCB, but also the internal connectors and interfaces to the outside world. The elegant integration of these complex interconnects in a highspeed way is my personal interest. The plan driven by reality today is to support the production ramp, work with customers to design their version of the technology and push the capability to the next node in 2019.

**Beaulieu:** What new products are your working on?

**Rathburn:** We are currently investing in two parallel paths. The first is engineering and applications support for Benchmark customers as the technology matures and is adopted into production. Benchmark has made significant investments in the launch technologies that will be available in production soon, but the engineering expertise to help the customers implement is a key future investment with software, simulation, high-speed and RF design rules, and practical application support.

The second investment is to extend the launch capability to the next process node with a key focus on not just the circuit fabrication, but the unique assembly techniques needed to integrate function and devices into the LCP circuit stack.

Shrinking from 20- or 25-micron circuit fabrication down to nine microns does not seem like a big shrink, but below 20 microns there is a significant process and capability shift that is not trivial.

Beaulieu: When will they be coming out?

Rathburn: The launch capabilities are in sample and qualification stages through 2018, and 2019 will bring the next technology node.

**Beaulieu:** Any last comments as we wrap up this interview?

**Rathburn:** In closing, HSIO is very proud to be in a position to enable our exciting technologies with Benchmark as our manufacturing partner, and our customers as our development partners. There is no other company, collaboration or technology I am aware of that can design, build and assemble a high layer count, high-density, high-speed LCP-based printed circuit with the ability to directly attach die or embed devices that normally function discretely. We are also very proud to be a foundational part of Benchmark's new RF High-Speed Center of Innovation and believe our vision and technologies are fulfilled in a way that makes Benchmark the new measure in the EMS industry.

Beaulieu: Thanks, Jim. PCB007

## A NEW QUARTERLY MAGAZINE

With original content dedicated specifically to flex system and PCB designers, electrical engineers and those responsible for integrating flex into their products at the OEM/CEM level, you won't want to miss a single issue of **Flex007 Magazine!**

**Subscribe**

**Contribute**

**Advertise**

## Smartphone Substrate-Like PCBs Will Revolutionize the IC Substrate and PCB Markets

Feature by Emilie Jolivet YOLE DÉVELOPPEMENT

The smartphone is one of the high value-add products that carries a very high demand for miniaturization. Customers expect larger screens, cameras with high resolution, and various other functions, in lighter and thinner phones. In 2017, Apple requested a new "board," a substrate-like PCB (SLP), for iPhones. This has resulted in a technology transition for the PCB manufacturers and the need to invest in a modified semi-additive process (mSAP). New competitors were also attracted to this field: IC substrate manufacturers who originated the mSAP technology.

As a result, there were high capital expenditures among the SLP suppliers for Apple. This was followed by Samsung; the Galaxy S9, released in early 2018, has also adopted SLP technology, and similar high capital invest-

ments were made by some Korean PCB manufacturers. Additionally, increasingly more PCB and IC substrate manufacturers that were not in Apple and Samsung's supply chain are joining the competition of fabricating SLPs.

Starting with the adoption of SLP late in 2017, the volume is expected to grow from 27 million units in 2017 to 440 million units by 2023 with a CAGR of 59.4%. The SLP revenue in 2017 is estimated to be \$190M and will grow to \$1.4B in 2018, then \$2.2B by 2023 with a CAGR of 51%<sup>[1]</sup>.

The interest in decreasing the feature size for a smartphone board is due to the demand for thinner but more functional smartphones. With increasingly more functions added, along with larger screens, the power consumption becomes a critical point. In the volume of a smartphone, the battery takes up most of the space. As the feature sizes on the board decrease, more integration can be achieved in a

#### FILLING YOUR CHALLENGES ONE VIA AT A TIME

#### BY TAIYO

#### THP-100 DX1 VF(HV)

- Texacteristics for Large Holes

THP-100 DX1 VF (HV)

#### THP-100 DX1 HTG

- ♥ Highest TG (173°C) Available on the Market

- **♥** Low CTE (19/55)

THP-100 DX1 (HTG)

## THP-100 DX1 (GF) GAP FILLING MATERIAL

- ♥ Low Warpage

- ♥ Easy to Process

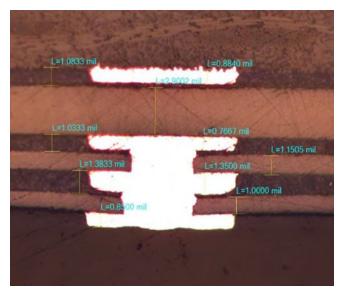

## Length = 0.26 mil

THP-100 DX1 (GF)

#### THP-100 (NEW VERSION)

- **Short Curing Time**

- Tow CTE for Better Back Drilling

Phone [775] 885-9959 • www.taiyo-america.com • info@taiyo-america.com

fixed area. As can be seen in Figure 1, starting from iPhone 5s, Apple has gradually decreased the PCB area of the iPhones compared to the total smartphone area. Until the latest iPhone X, they have decreased 3% of the area while adding more functions and increasing the battery capacity. In the meantime, iPhone X not only adapted SLP but also stacked two SLPs like a sandwich to further increase integration in a fixed area.

This surface reduction was enabled by the increase of density and reduction of interconnection.

The semiconductor industry's trends are affecting the semiconductor package and package-to-board interconnect level. PCB traditionally serves as the interconnection of the chips and the final product, but nowadays it is also an integration solution. SLP is one of the answers today to the scaling demand while also responding to the functional roadmap.

SLP is so-named because this "board" has blurred the definition between a PCB and an IC substrate. Although usually fabricated by different technologies, the main difference between a PCB and an IC substrate is the feature sizes, especially line and space (L/S). Traditionally a PCB or even HDI board has feature sizes greater than 30/30 mm; an IC substrate, on the other hand, has L/S that is often > 15/15 µm. Nevertheless, SLP has reached L/S that is smaller than 30/30 µm, and this has defined the name for SLP as it is a PCB that has the feature sizes close to that of an IC substrate.

Traditionally, PCBs are fabricated using a subtractive process that requires etching the preexisting copper-clad laminate (>5 µm thickness). This often results in over-etching that cannot be compensated for afterwards. As a result, the minimum L/S using this technology is limited.

Different from the subtractive process, mSAP uses a negative pattern design to "grow" copper by electroplating on top of the pre-existing thin copper clad (<5 µm thickness, which serves only as the seed). Then the negative pattern is etched. mSAP is usually used for IC substrate fabrication and allows a further miniaturization of feature size for L/S. Until now, within the few smartphone models that have already adapted SLP, the L/S remains around 30/30 µm. However, the adaptation of mSAP for board is to further decrease L/S to increase

| Apple Models                                                               | iPhone 5S   | iPhone6     | iPhone 6S                                               | iPhone 7                                                | iPhone 8              | iPhone X                           |

|----------------------------------------------------------------------------|-------------|-------------|---------------------------------------------------------|---------------------------------------------------------|-----------------------|------------------------------------|

| Flagship Model                                                             |             |             |                                                         | ÷                                                       |                       | 09:41                              |

| PCB Analyzed<br>(System Plus<br>Consulting)<br>Main Board – Front<br>Side) |             |             | Not Analyzed<br>(considered pretty<br>close to iPhone6) | Not Analyzed<br>(considered pretty<br>close to iPhone6) |                       |                                    |

| Phone Surface<br>(mm²)                                                     | 7254.68     | 9252.7      | 9279.93                                                 | 9279.93                                                 | 9314.32               | 10181.24                           |

| Phone thickness<br>(mm)                                                    | 7.6         | 6.9         | 7.1                                                     | 7.1                                                     | 7.3                   | 7.7                                |

| PCB Surface (mm²)                                                          | 1517.97     | 1834.73     | 1834.73                                                 | 1834.73                                                 | 1800                  | 1849.2                             |

| Ratio (PCB<br>area/.Phone area)                                            | 21%         | 20%         | 20%                                                     | 20%                                                     | 19%                   | 18%                                |

| Technology                                                                 | Subtractive | Subtractive | Subtractive                                             | Subtractive                                             | Subtractive<br>+ mSAP | Sandwich PCB<br>Subtractive + mSAP |

Figure 1: PCB analysis of Apple flagship smartphones.

Figure 2: Advanced substrate technology segmentation projection.

integration. There are still challenges in adapting mSAP for board fabrication; current SLPs are not fully fabricated by mSAP but a mixture of subtractive and mSAP (Figure 2). Research and development is being done to gain more control of the fabrication process and further decrease feature sizes.

Figure 2 shows the vision of the advanced substrate technology segmentation regarding the demanded featured size. As can be seen, technologies that are traditionally used for different manufacturing steps start to overlap. SLP today gives an example of packaging technology used for board fabrication, in the future, other technologies will overlap as well and create potential new field of competition in the semiconductor industry.

Although only two smartphone manufacturers have adapted SLP to their flagship phones, it is expected that other large smartphone manufacturers such as Huawei, Xiaomi, and Vivo will follow this trend in the next few

years. Smartphone manufacturers will continue the tendency of increasing integration in a fixed board area to add functions or to provide space for additional battery capacity. Other products that require strong miniaturization such as wearables, tablets, and tablet-PCs will most likely be the next products to adopt SLP.